컴퓨터가 등장하던 1940년대부터, 아니 어쩌면 명제를 고민했던 고대 그리스 시대부터 우리는 ‘참’과 ‘거짓’으로 이뤄진 이분법 시대에 살고 있다. 세상에 많은 명제들은 0과 1로 충분히 설명이 가능했고, 컴퓨터 역시 무리 없이 약 2년마다 두 배씩 성능을 높여왔다(무어의 법칙).

참과 거짓만으로 표현되던 세상이 무너지다

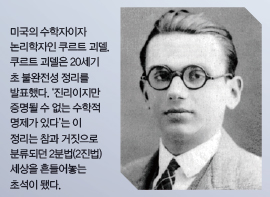

견고한 철옹성 같은 2진법이 위협을 받기 시작한 건 20세기 초 미국의 수학자이자 논리학자인 쿠르트 괴델이 ‘불완전성 정리’를 발표하면서부터였다. 수학자들도 이해하기 어렵다는 불완전성 정리의 골자는 ‘진리이지만 증명될 수 없는 수학적 명제가 있다’는 것이다. 여기에서부터 참과 거짓 두 개로 나뉘어 있던 세계는 조금씩 무너져갔다.

불완전성 정리는 ‘양상 논리(Modal Logic)’로까지 확장되는데, 이는 명제를 필연성, 가능성, 불가능성으로 나눈 논리 체계다. 예를 들어 ‘나는 곧 집에 갈 것이다’라는 명제가 있다면 나는 아직 집에 가지않았으니 참이라고 할 수 없지만, 곧 갈 수도 있으니 거짓이라고 할 수도 없다. 이런 명제는 ‘가능성’으로 분류할 수 있다. 진릿값이 두 개가 아닌 세 개가 된 것이다.

이런 바람은 컴퓨터 분야로까지 퍼졌다(수학과 컴퓨터는 뗄래야 뗄 수 없는 사이다). 마침 무어의 법칙도 슬슬 힘에 부치기 시작한 시기였다. 획기적으로 집적도를 높일 무언가가 필요했고, 3진법과 그이

상의 n진법이 각광받기 시작했다.

참과 거짓만으로 표현되던 세상이 무너지다

견고한 철옹성 같은 2진법이 위협을 받기 시작한 건 20세기 초 미국의 수학자이자 논리학자인 쿠르트 괴델이 ‘불완전성 정리’를 발표하면서부터였다. 수학자들도 이해하기 어렵다는 불완전성 정리의 골자는 ‘진리이지만 증명될 수 없는 수학적 명제가 있다’는 것이다. 여기에서부터 참과 거짓 두 개로 나뉘어 있던 세계는 조금씩 무너져갔다.

불완전성 정리는 ‘양상 논리(Modal Logic)’로까지 확장되는데, 이는 명제를 필연성, 가능성, 불가능성으로 나눈 논리 체계다. 예를 들어 ‘나는 곧 집에 갈 것이다’라는 명제가 있다면 나는 아직 집에 가지않았으니 참이라고 할 수 없지만, 곧 갈 수도 있으니 거짓이라고 할 수도 없다. 이런 명제는 ‘가능성’으로 분류할 수 있다. 진릿값이 두 개가 아닌 세 개가 된 것이다.

이런 바람은 컴퓨터 분야로까지 퍼졌다(수학과 컴퓨터는 뗄래야 뗄 수 없는 사이다). 마침 무어의 법칙도 슬슬 힘에 부치기 시작한 시기였다. 획기적으로 집적도를 높일 무언가가 필요했고, 3진법과 그이

상의 n진법이 각광받기 시작했다.

‘가성비’ 좋은 3진법, 현재로서는 가장 가능성 높아

1파트에서 확인했듯 3진법 소자들은 다양한 형태로 연구되고 있다. 그런데 소자만 개발된다고 모든 문제가 끝나는 것일까. 하드웨어가 마련됐다고 컴퓨터가 저절로 작동하는 것이 아니듯, 3진법 소자를 반도체로 이용하려면 이를 적용시킬 수 있는 회로 설계가 필요하다.

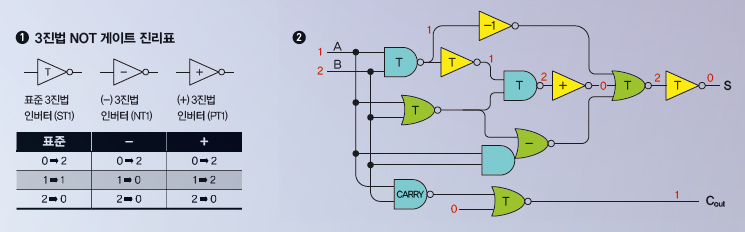

그런데 말처럼 쉽지는 않다. 현재 우리가 사용하고 있는 회로는 기본적으로 ‘AND’, ‘OR’, ‘NAND’, ‘NOR’, ‘NOT’ 게이트로 이뤄진다. AND 게이트를 예로 들면 입력 값이 둘 다 1일 때를 제외하고는 출력 값이 모두 0인 게이트이며, NOT 게이트는 이름에서도 알 수 있듯이 입력 값이 0이면 1, 1이면 0을 출력한다. 자, 이제 3진법을 적용시켜보자. NOT 게이트에 0이 들어가면 무엇이 나와야 할까.

다행히 3진법 소자를 개발하는 이들이 합의한 논리 게이트들이 있다(위 진리표 참고). 이 게이트들을 바탕으로 회로를 설계해야 한다. 4진법, 8진법 등 n진법에 대한 논리 게이트 역시 연구돼 있지만, 그 중 3진법이 가장 많이 연구된 이유는 ‘가성비’ 때문이다. n이 1씩 커질 때마다 데이터 처리 능력은 높아지고 회로 복잡도는 줄어드는데, 3진법이 가장 높은 효율을 보인다. 2진법에 비해 3진법은 n비트를 기준으로 데이터 처리 능력이 (1.5)n배 커지고, 같은 데이터를 처리하기 위해서 필요한 소자나 회로 연결은 63.1%로 줄일 수 있다(더 읽을 거리 참조).

3진법 소자를 지지해줄 인프라 구축이 필요하다

국내에서도 3진법에 맞는 논리 회로를 설계하는 연구자가 있다. 강석형 UNIST 전기전자컴퓨터공학부 교수는 최근 더욱 효율적인 3진법 덧셈기와 곱셈기를 설계했다. 3진법 연산을 하려면 그에 맞는 덧셈기, 뺄셈기, 곱셈기 등 논리 연산 장치(ALU)가 필요하다. 강 교수는 “기존에 제안됐던 덧셈기의 경우 2진 소자를 기반으로 회로를 구현하려고 했기 때문에 회로가 아주 복잡했다”며 “이번 연구는 0, 1, 2라는 입력값을 다시 2진법으로 변환해 계산하는 방식을 탈피해 복잡도를 획기적으로 줄였다”고 말했다.

하지만 덧셈기와 곱셈기는 설계의 기본에 불과하다. 강 교수는 “아직 3진법 소자를 개발하는 중이라 완벽한 논리 회로를 설계하기가 힘들다”며 “세계적으로 3진법 회로 설계를 연구하는 사람이 많지는 않다”고 말했다. 강 교수는 국내의 유일무이한 3진법 회로 설계 연구자다.

“아직 갈 길이 멉니다. 3진법 소자가 개발된다 하더라도 이에 맞는 소프트웨어는 아직 이론적인 연구수준을 벗어나지 못했고, 시스템 단위의 아키텍처 설계 또한 지연되고 있습니다. 3진법 소자 개발이 가장 우선이지만 그 다음 단계의 연구까지도 함께 이뤄져야 3진법의 패러다임을 맞이할 수 있습니다.”

1파트에서 확인했듯 3진법 소자들은 다양한 형태로 연구되고 있다. 그런데 소자만 개발된다고 모든 문제가 끝나는 것일까. 하드웨어가 마련됐다고 컴퓨터가 저절로 작동하는 것이 아니듯, 3진법 소자를 반도체로 이용하려면 이를 적용시킬 수 있는 회로 설계가 필요하다.

그런데 말처럼 쉽지는 않다. 현재 우리가 사용하고 있는 회로는 기본적으로 ‘AND’, ‘OR’, ‘NAND’, ‘NOR’, ‘NOT’ 게이트로 이뤄진다. AND 게이트를 예로 들면 입력 값이 둘 다 1일 때를 제외하고는 출력 값이 모두 0인 게이트이며, NOT 게이트는 이름에서도 알 수 있듯이 입력 값이 0이면 1, 1이면 0을 출력한다. 자, 이제 3진법을 적용시켜보자. NOT 게이트에 0이 들어가면 무엇이 나와야 할까.

다행히 3진법 소자를 개발하는 이들이 합의한 논리 게이트들이 있다(위 진리표 참고). 이 게이트들을 바탕으로 회로를 설계해야 한다. 4진법, 8진법 등 n진법에 대한 논리 게이트 역시 연구돼 있지만, 그 중 3진법이 가장 많이 연구된 이유는 ‘가성비’ 때문이다. n이 1씩 커질 때마다 데이터 처리 능력은 높아지고 회로 복잡도는 줄어드는데, 3진법이 가장 높은 효율을 보인다. 2진법에 비해 3진법은 n비트를 기준으로 데이터 처리 능력이 (1.5)n배 커지고, 같은 데이터를 처리하기 위해서 필요한 소자나 회로 연결은 63.1%로 줄일 수 있다(더 읽을 거리 참조).

3진법 소자를 지지해줄 인프라 구축이 필요하다

국내에서도 3진법에 맞는 논리 회로를 설계하는 연구자가 있다. 강석형 UNIST 전기전자컴퓨터공학부 교수는 최근 더욱 효율적인 3진법 덧셈기와 곱셈기를 설계했다. 3진법 연산을 하려면 그에 맞는 덧셈기, 뺄셈기, 곱셈기 등 논리 연산 장치(ALU)가 필요하다. 강 교수는 “기존에 제안됐던 덧셈기의 경우 2진 소자를 기반으로 회로를 구현하려고 했기 때문에 회로가 아주 복잡했다”며 “이번 연구는 0, 1, 2라는 입력값을 다시 2진법으로 변환해 계산하는 방식을 탈피해 복잡도를 획기적으로 줄였다”고 말했다.

하지만 덧셈기와 곱셈기는 설계의 기본에 불과하다. 강 교수는 “아직 3진법 소자를 개발하는 중이라 완벽한 논리 회로를 설계하기가 힘들다”며 “세계적으로 3진법 회로 설계를 연구하는 사람이 많지는 않다”고 말했다. 강 교수는 국내의 유일무이한 3진법 회로 설계 연구자다.

“아직 갈 길이 멉니다. 3진법 소자가 개발된다 하더라도 이에 맞는 소프트웨어는 아직 이론적인 연구수준을 벗어나지 못했고, 시스템 단위의 아키텍처 설계 또한 지연되고 있습니다. 3진법 소자 개발이 가장 우선이지만 그 다음 단계의 연구까지도 함께 이뤄져야 3진법의 패러다임을 맞이할 수 있습니다.”