라디오같은 간단한 전자제품을 직접 조립해 본 사람이라면 처음 보는 회로가 너무 복잡해 보여 혼란스러웠던 경험이 있을 것이다. 그래도 설명서나 교사의 지도를 따라 조금씩 부품을 맞춰나가다 보면 차츰 구조와 원리를 익히게 된다.

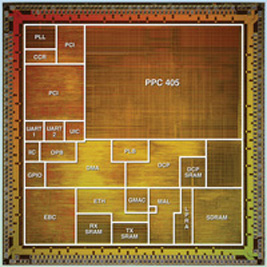

그러나 요즘 컴퓨터에 사용되는 마이크로프로세서는 라디오에 들어가는 트랜지스터의 개수와는 비교도 안 될 만큼 많다. 지난해 개발된 IBM의 서버용 프로세서 ‘Power5’에는 2억7600만개의 트랜지스터가 집적돼 있다. 이쯤 되면 칩 설계는 사람이 하나하나 짜 맞출 수 있는 범위를 넘어선다. 회로를 구성하는 단위가 너무 복잡해지기 때문이다.

새는 전류 막아 저전력 칩 설계한다

“반도체 칩 설계에 컴퓨터를 이용하면 시간과 비용을 크게 절약할 수 있습니다.”

KAIST 전자계산학과 신영수 교수와 VLSI디자인기술연구실 학생들은 컴퓨터를 이용한 자동 설계 기술로 반도체 칩을 디자인하는 방법을 연구한다.

VLSI(초대규모 집적회로)는 실리콘 기판 위에 100만개 이상의 소자가 집적된 회로다. 오늘날 사용하는 컴퓨터의 마이크로프로세서는 모두 VLSI다.

VLSI 반도체는 라디오처럼 트랜지스터를 하나씩 맞춰가는 방법으로는 설계하는데 시간과 공력이 너무 많이 든다. 따라서 컴퓨터를 이용해 특정 기능을 담당하는 부분들을 조합하는 방식으로 칩의 전체 구조를 설계한다.

“반도체 칩 설계에서 가장 중요한 것은 전력소모를 줄이고 집적도를 높이는 기술입니다. 다양한 휴대 전자기기에서 ‘더 가볍게’를 추구하는 경량화 추세가 확산되면서 저전력 설계의 필요성이 계속 커지고 있습니다.”

연구팀이 초점을 맞추고 있는 연구도 칩에서 전력을 적게 소비하는 기술이다. 현재 연구 중인 ‘파워 게이팅 프로젝트’는 반도체 칩에서 누설(漏泄)전류 때문에 발생하는 전력소모를 줄이기 위한 기술이다. 전기가 통하지 않는 절연체도 전압을 가하면 아주 미세한 전류가 흐르는데, 이를 ‘새어 나간다’는 뜻에서 누설전류라고 부른다. 누설전류가 커질수록 기기를 작동시키는데 사용할 수 있는 전력이 줄어들기 때문에 이 손실을 줄이면 저전력 반도체를 설계하는 데 큰 도움이 된다.

최적의 설계 기술을 찾아라

신 교수는 지난해 3월 ‘고품질 전자설계에 관한 국제 심포지엄’(ISQED)에서 ‘마스크 재사용을 통한SoC 설계비용 감소 기법’이란 논문으로 국제전기전자기술협회(IEEE) 컴퓨터연구회가 수여하는 ‘최고 논문상’을 받았다.

‘시스템온칩’(SoC, System-on-a-Chip)이란 과거엔 따로 꽂아야 했던 컴퓨터의 사운드 카드나 그래픽 카드가 메인보드에 모두 통합된 것처럼 반도체칩 하나에 완성된 시스템이 모두 들어간 것이다.

기존 반도체 설계에서는 먼저 회로 패턴을 설계해 유리판 위에 그린다. 이것을 ‘마스크’(mask)라고 한다. 이 마스크를 이용해 반도체 재료인 웨이퍼 위에 회로를 그려 넣는다. 칩을 하나 설계할 때마다 마스크를 새로 만들어야 한다. 당연히 시간과 비용이 많이 든다.

그러나 신 교수는 칩의 구성 요소들을 미리 각각의 마스크로 만들어 뒀다가 설계에 따라 필요한 마스크를 가져와 정렬하는 방법으로 전체를 제작하는 새로운 방법을 제안했다. 활자를 조합해서 책을 인쇄하는 것과 비슷한 원리다. SoC 설계 시간을 줄이고 마스크 제작비용을 대폭 줄일 수 있는 독창적인 방법이라는 점이 최고 논문상감으로 높이 평가받았다.

신 교수는 서울대 전자공학과를 졸업하고 2000년 박사학위까지 모두 동 대학원에서 받은 토종 국내파 엔지니어다. 2001년부터 IBM 왓슨연구소에서 근무할 때 많은 아이디어를 얻었다.

초고집적 SoC 개발을 위한 설계 시스템 개발이나 최고 논문상을 안겨 준 마스크 재사용 기법도 IBM에서의 연구를 바탕으로 얻은 성과다. 그는 현재까지 국내외 학술지에 40여편의 논문을 발표했다.

신 교수가 KAIST 전자전산학과 교수로 온 것은 지난 2004년 7월이다. 신생 연구실이라 아직 연구원은 4명(박사과정 1명, 석사과정 3명)뿐이지만 이들은 “연구가 재미있어서 사람 수가 적은 것은 아무 문제도 되지 않는다”고 말한다.